基本变址机构

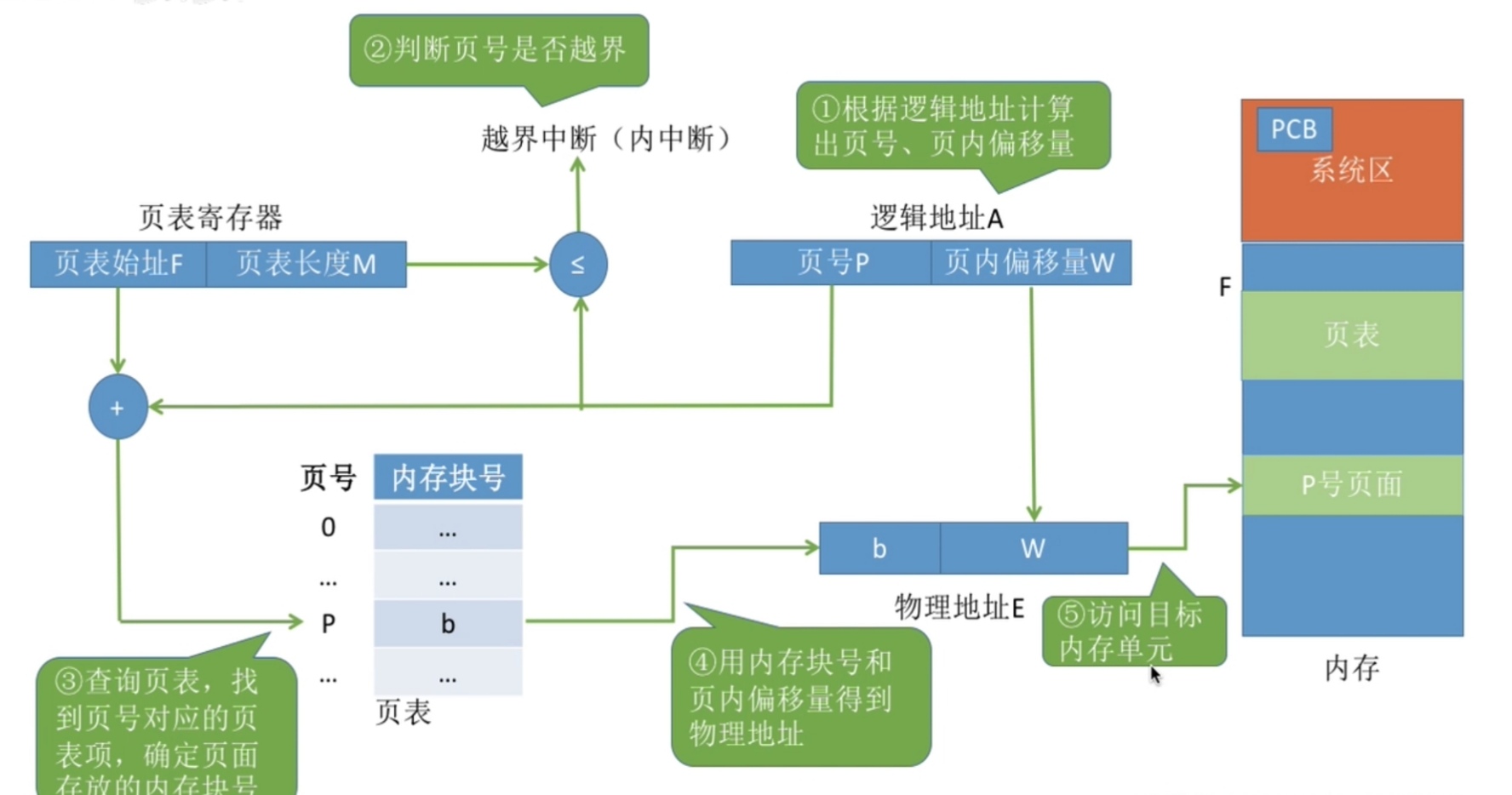

基本变址机构(两次访存)解决分页存储地址转换问题的,通常会在系统中放置一个页表寄存器来存放页表在内存中的起始地址F和页表长度M,进程未执行时,页表的始址和页表长度会放在进程控制快中,当进程调度时,操作系统内核会把他们放在页表寄存器里,具体流程看下图

在你仔细看完这个流程图后我想你大概会有这样的几个问题,

那个小于等于号为什么要有等于–因为页表长度最小是1,而页号最小是0,因此当页号是1,实际上他的页表长度已经是2了,因此越界;

为什么需要将页号和页表始址连接起来–因为也表示放在内存里的,我想读页表我得先找到他。

bw是什么–你可以去看看在分页存储那里讲的操作系统怎么简单的获得页号和页内偏移量

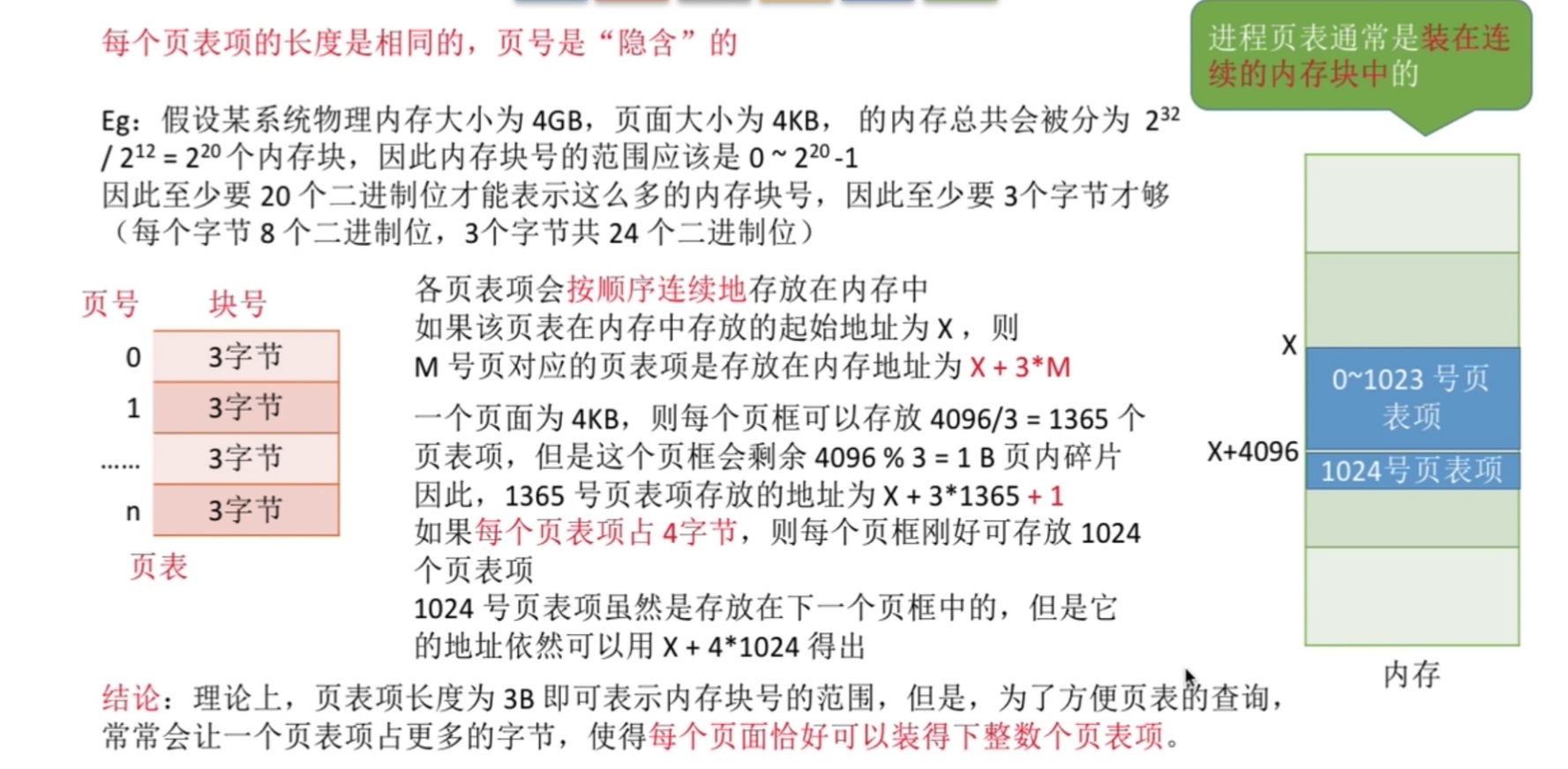

下面来深究一下页表项长度问题

出现上图问题的原因实际上是因为,我本来要20位就够了,但为了凑字节,我只能再加四位,如果我用3个字节表示页表号,那我一个页框可以存1365个页表项,还剩1个字节的碎片啥也装不了,那我1365号(第1366个)就只能在下一个页框里存了,那我就不能直接用之前的结论,我还得再加1,为了解决这个问题,我可以让页表项占更多的字节,这样的话就不会出现碎片

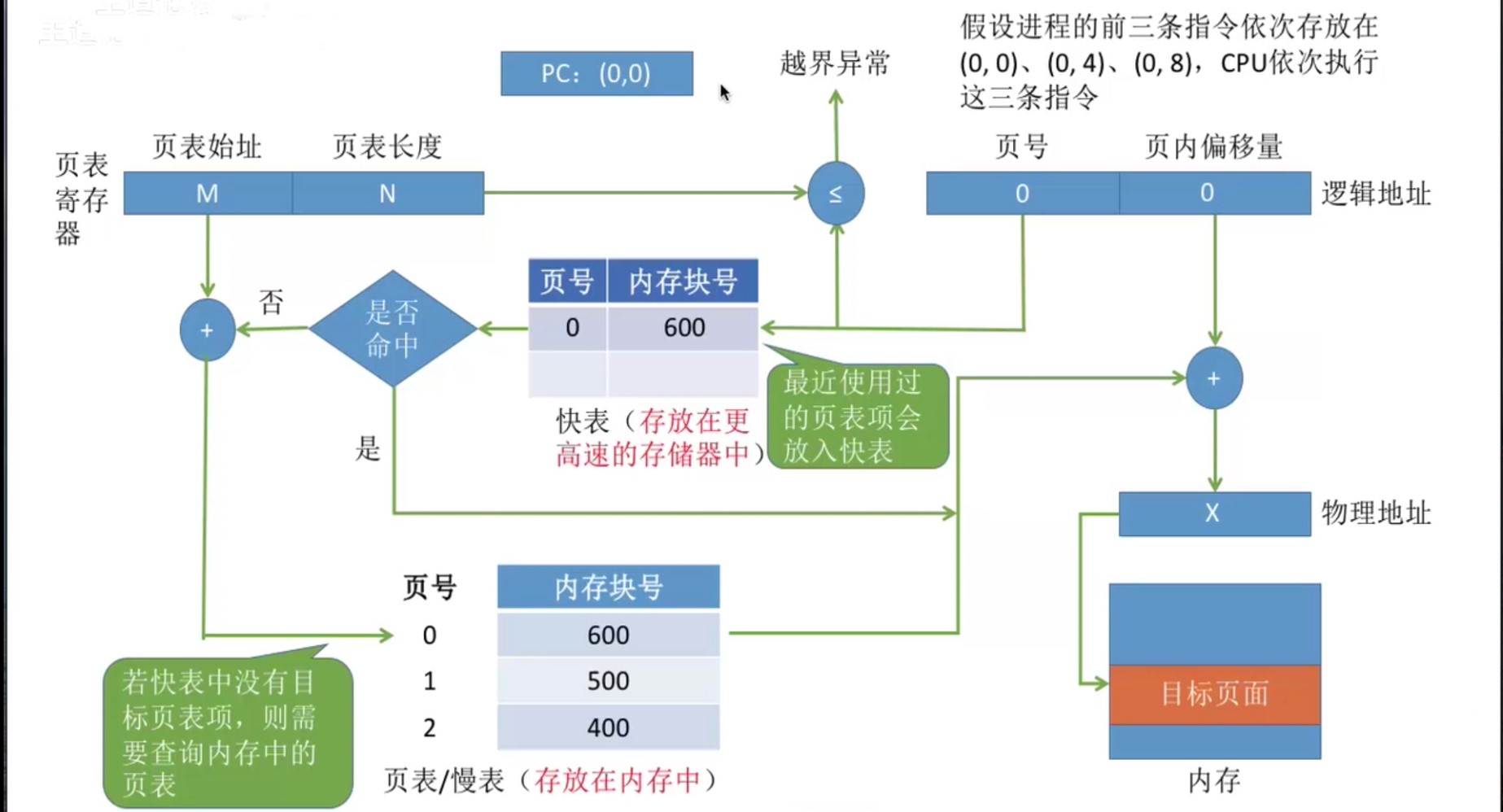

具有快表的地址变换机构

具有快表的地址变换机构实际上是基本变址机构的一个完善

首先先来看看两个概念

时间局限性:如果执行了程序中的某条命令,那么不久后这条命令很有可能被再次执行;如果某个数据被访问过那么他很有可能在不久后被再次访问(比如程序中有大量循环)

空间局限性:一旦程序访问了某个存储单元,在不久后,它附近的存储单元也很有可能被再次访问(比如数据是连续存放的)

基本的地址变址机构需要每次都查页表,很有可能好几次连着查的都是同一个页表项

增加一个快表就能解决这个问题

快表(TLB),又称联想寄存器,是一种访问速度比内存快很多的高速缓冲寄存器,用来存放当前访问的若干页表项,以加速地址变换过程,与此对应,内存中的页表又叫做慢表

如图所示(0,0)先进,前后两个0分别表示页号,偏移量

刚开始的时候快表为空,所以会在页表中查找,与此同时会存在快表中如上图所示

等到执行(0,4)时,因为还是在0号所以就不必再查找,直接在快表里拿出来用就行了,剩下的以此类推

若快表满了,则必须按照一定的算法对旧的页表项进行替换(页面置换)

这样我们就可以很清楚的看出来,如果快表命中,那变址速度就会显著提高,一般来说快表命中率在90%以上

我们来算算看

若访问快表时间为1微秒,访问内存为100微秒,快表命中率为90%,那么访问一个逻辑地址的平均耗时是多少

a. 快表慢表不同时访问

(1+100)0.9+(1+100+100)0.1=111微秒

第一个一百为对内存访问,第二个也是,第三个是对慢表访问(快表命中,一次访存;快表未命中,两次访存)

b. 快表慢表同时

(1+100)0.9+(100+100)0.1=110.9微秒

同时时快表那1微秒就省了

c. 若未采用快表

100+100=200微秒